选择上拉电阻

当端口引脚为逻辑“0”时,输出电压接近地电平。在该状态下,电流将通过上拉电阻和端口驱动器流入地。为了减小功耗,我们希望用一个大阻值的电阻使这个电流最小。

当端口引脚为被设置为逻辑“1”,输出驱动器关断,端口的输出通过一个上拉电阻被拉为高电平。号的上升时间可能很长,由上拉电阻值和寄生电容值所决定。寄生电容包括连线电容和输入电容。在图1所示的电路中,5V电源通过上拉电阻给寄生电容充电,充电时间常数为寄生电容与上拉电阻的乘积:

如果时序并不重要(例如,按钮或片选信号),则充电时间的影响不大。但是如果时序显得重要(例如,串行通信和时钟信号同步),则必须要考虑充电时间,这就要限制上拉电阻的最大值。上拉电阻的阻值大将导致对寄生电容的充电时间长,因而端口引脚电压上升到实现逻辑“1”所需的高电平的时间就长。参见下面的图2,其中:T是为充电到高于5V器件实现逻辑“1”所要求的高电压(通常称为Vih)而花费的时间。这个电压值与寄生电容一样,取决于应用系统的实际情况。如果时间常数过大,5V器件在给定的方波周期内可能永远接收不到足够高的电压来实现逻辑“1”。因此,为了得到正确的输入,所选择的上拉电阻阻值必须足够小,但为了保证在逻辑“0”状态上拉电阻不消耗过多的功率,阻值又不能太小。

对于一个给定的应用,一旦可接受的最大上升时间(T)确定,可以通过解方程1来计算上拉电阻 (R) 的值:

尽管输出电压从高降到低(“1”到“0”)有一个小的延时,但该时间与上升时间相比微不足道。图2中显示出(尽管已经对该时间放大)这个很小的衰减时间。寄生电容中的电荷通过C8051Fxxx的端口驱动器放电到与地电平相差很小的电压值。

如前所述,如果上拉电阻小,则在逻辑“0”状态电流从5V电源流入地时将有大的功率消耗。另外,如果该电阻值过小,由于端口驱动器存在电压降落,可能会因低电平状态的电压过高而不能实现逻辑“0”(Vol)。例如,对于C8051F0xx器件,其Vol指标在8.5mA时为0.6V。小电阻会导致较的电流,从而对5V器件产生较高的输入电压。

概括来说,上拉电阻必须是:

- 足够大,以避免在逻辑 0 状态产生过大的电流和功耗

- 足够大,使电压低于5V器件的Vil以实现逻辑 0 状态

- 足够小,根据寄生电容和应用要求提供可接受的上升时间

示例

下面是一个在已知寄生电容(C)、所要求的逻辑“1”(Vih)电压电平以及状态转换频率(它决定了所允许的最大上升时间(T))的情况下计算上拉电阻(R)的例子。我们还要计算逻辑“0”状态下上拉电阻消耗的功率和电压电平。我们将据此选择上拉电阻(R)的值。

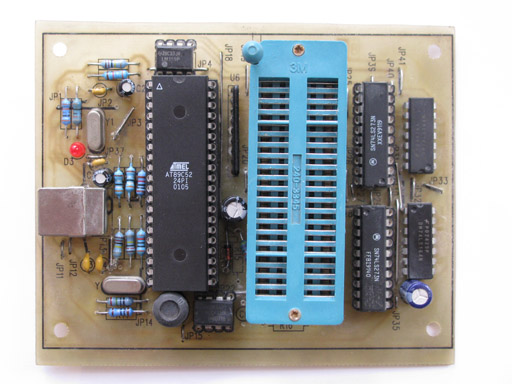

在本例中,我们将考虑使用SMBus的一个应用:C8051Fxxx在主方式(提供SCL信号给其它器件)下输出漏极开路同步时钟信号(SCL)。该信号作为一个5V器件的输入,为了保证能提供正确的电压,我们使用第二页中图1所示的配置。要保证在采用这一方法时所用的端口引脚被配置为漏极开路(见相关的数据表)。C8051Fxxx在复位后端口引脚的缺省设置为漏极开路。

必须计算一个合适的上拉电阻值,以保证:

- 逻辑“0” 状态下的电流/功耗最小。(R值过小 )

- 由寄生电容和上拉电阻决定的上升时间在规定的性能指标之内。(R值过大 )

- 在逻辑低电平状态,端口驱动器上的电压降不会过大。(R值过小 )

在低功耗应用中(即,使用电池供电的情况),使用大电阻是比较理想的,可以使功耗最小。我们将计算满足电压上升时间要求的最大电阻值。对于本应用,电压应在时钟周期的5%时间内上升到5V器件的CMOS逻辑高电平。我们假定 Vih 为0.8×VDD,或4伏。选择SCL频率为400kHz,我们的电压应在125ns内上升到4伏。

将T=125ns、Vih =4伏代入方程2中。我们假设寄生电容为10 pF,只有一个从器件挂在SCL线上。(这会随着应用不同而变化,取决于所连接的器件数和连接这些器件所用的连线的数量)。我们用方程2计算得R=7.77 kΩ。这是满足给定的SCL频率和我们所设定的CMOS输入高电平的最大上拉电阻值。注意,SCL的频率越低,上拉电阻值就可以越大。

注意,我们已经有了所希望的最大电阻值。我们可以计算逻辑“0”状态时流过电路的电流,看这个电流对一个给定的应用来说是否可以接受。考虑最坏的情况,我们计算在电源电压为5V且端口引脚与地之间的电压降可以忽略不计的情况下的电流。这样,流经7.77 kΩ电阻的电流为644µA。在流过644 µA的电流时上拉电阻消耗的功率约为3.2 mW。