FPGA的公司实际上换而言之,也可以成为EDA的公司了,只是他们在这方面的能力是否强大而已.这3家公司中,拥有自己HDL的公司只有Altera.可能很多人不太清楚,就是AHDL,当然这种语言的辉煌期已经过去了.这里说这个,绝对不是鼓励大家用这个语言.

这3家主要的开发软件大家都知道,在中国应该以Quartus II用的最广.ISE次之.但是现在这两大软件的外观都已经有些一致的地方了.但是他们近乎同样外观的软件,却还是有很多地方非常不同.

Altera 在2000年前,在日本市场独领风骚.大家知道日本是漫画的国度,他们总是喜欢用图形表达,这可以证明Altera的图形输入做的是炉火纯青.但是,现在都是语言输入为主导了,因此Altera的这个优势才渐渐淡化.但是其他图形界面仍旧有其鲜明的特色,简单容易.

Altera的软件像Canon的相机,很傻瓜,对着景物按个快门.当然也有些地方,你也可以仔细微调.

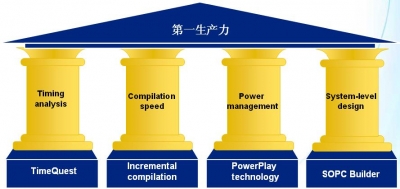

Xilinx的软件洋洋洒洒,很专业,像部哈苏相机,你在照相前,先成为相机的专家,才能成为设计的专家.有人开玩笑了,这是拿东西来说事.那在这里引用Altera公司一些思想,给大家介绍一下.实际上,这个特点非常容易记忆.大家都知道TIPS这个单词吧,就是提示的意思.那在这里就给你一些提示,让你可以过目不忘!

TIPS---提高设计效能的秘方!

这几天准备一下,尽快让大家看到下面的章节!

从TIPS中的T开始说,FPGA的趋势如下

1--首先说一下眼前的大环境是怎么影响你的设计的.过去的设计规模应该是比较小,一个FPGA工程师,写个状态机,写个好的代码,这个就是相对来说的高手了.但是你要知道这种高手都是关起门来自称老大的.实际出门走多远很难说.因为现在器件的发展速度是很快的.

2---规模的变化

1998---一位当时的PLD的厂商说 世界上有1000个宏单元的PLD就可以应付95%的设计了.今天你认为怎样?

1998---最大的FPGA内含10000LEs,今天的CycloneIII的第二小的家伙就是这个身段.

2008年---现今最大的FPGA内含530,000LEs,比1998年增大50倍!你还能用以前的设计方式来应付今天这个庞然大物吗?

3---规模的变化,带来复杂度的提高,调试也成为关键?

芯片规模大的时候,你就会要有些测试工程师的需求.因为人自己总是看不清自己的缺点.

4---一个模块跑个固定的速度,是否可以和其他模块都配合起来,还能保持性能?

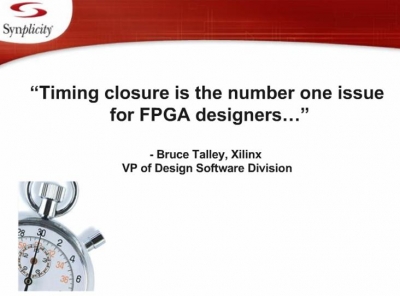

目前EDA厂商众口一辞的话: 20KLEs规模以上的设计,时序收敛是第一目标

当有问道Xilinx的软件设计者时候 ,他们也承认了这样的事实:

好了,第一个题目诞生了.T-IPS 中的T就是TimeQuest,以前FPGA的规模和设计ASIC不能相比,今天已经可以了.在FPGA中集成很多IP已经不是什么难题了.TimeQuest是依照SDC来进行工作的,SDC,是ASIC中设置约束的工具,换言之,也算是你如何指挥你的软件,将你设计的模块让他们统一协调好时间,然后保证最终的结构是你想要的.你不仅要看到设计,还要跑到那样的速度的时候,他还是你要的功能 ,有人说了,以前没有这样的工具吗? 有,但是那不是针对大的设计的.当然大也是相对的,到了一定的规模,就必须使用另外的标准了! 什么能帮助你达到时序收敛,什么可以加速你找到哪些地方不满足,TimeQuest!

目前支持这个SDC的有以下工具,当然Quartus支持的最完整. 潜在的秘密是,Altera的器件的规模也是最大的了.

- Altera -TimeQuest à SDC based Timing analysis

- Actel – Offers preliminary SDC support

- Xilinx & Lattice – No SDC support

可能你会问,能不能详细点说一下:

- TimeQuest是Altera第二代的时序分析工具

- 你不需要记忆什么语法,完全的GUI界面,而且也支持模板输入功能.

- 他生成的约束是基于Synopsys的工业标准的.

TIPS中的I是指"递增编译",就是英文"Incremantal compile"的第一个字母是I.

刚才说了,当你有时候改动了一部分设计的时候,你以前好不容易调好的时序,可能因为重新改动的影响,而在编译路由后,将没有改动的设计在布局和速度上发生了不期望的改变.那这个递增编译就是干这个的.他可以向制导武器一样,让你指哪里,打哪里.同时缩短编译时间,提高你的工作效率!当然这里绝非这么一句话就可以涵盖了.你也要有设计分离,规划布局等工作.

现在经常有提到我的产品是最好的Price,但是,现在由于系统规模增大,Power也是一个很重要的制约,功耗在某些设计中甚至是第一位的.Quartus中有关于根据Power的要求来智能编译设计的约束.就是TIPS中的P,也就是PowerPlay.

最后一个TIPS中的S就是指Systemlevel,或者是SOPC,因为你的设计可能要有各种接口,外部的,内部的,系统的互联.总线的对接,时钟域的交叉,这些,都可以用SOPC的工具SOPC builder来实现.不用内置处理器也可以.同时要求你在系统级的高度进行设计,这样就提高设计速度.在第三篇中有详细讲.

生产力发展的标志-生产工具,你现在和15年前设计方式的根本改变!

不管A,X,L,哪一家FPGA玩家,这三年来都在开发工具上投入了重兵.此前有网友争论--

Lattice用的是Synplify进行的综合,效果如何如何高.这个论调10年前是天经地义,颠覆不破的真理,但是今天再这样说,绝对偏颇!

Synplicity公司不少人后来都转投Altera门下.当时Sy最先得到Xilinx的结构的时候,大力发展所谓物理综合等一系列亮点,但是却对Altera提及甚少,大家都知道Sy的发家史,失去了FPGA厂商的支持,基本上也就失去温床.在2004年QuartusII4以后,Quartus的综合能力就已经与S家的不相伯仲了.Xilinx在10年前收购多家EDA厂商,例如StateCAD,当时用流程图生成状态机的VHDL和其他的一些厂商的时候,Quartus都是建立在自己的固有体系下.如果单独从产品器件上,只有工艺和功耗是未来需要争斗的地方,那么,综合能力和相关路由(就是紧耦合的模块放在一起)能力,以及EDA工具的全面性才是真正FPGA厂商的绝对命门.S家一共有250个软件开发人员.A家可能就远远不止了.

另外Cadence,Synopsys,Magma,Mentor等大哥,也就是卖个综合和核对工具,价值点相信大家已经悟到几分吧.

QuartusII 在今天,作为FPGA摄影大师的工具来说,不仅是精密的哈苏,更是Canon门下Eos MarkII的便捷傻瓜的代表.QuartusII就是今天FPGA的第一生产力