3 VHDL设计操作指南

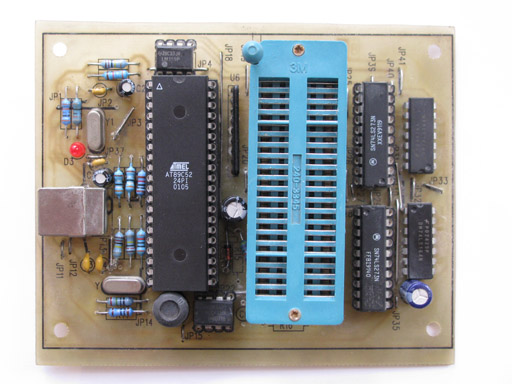

首先进入ISE工程管理器(Project Navigator)界面,如图4.30所示。 Project Navigator是ISE所用集成工具的连接纽带,通过使用Project Navigator,设计者可以创建、组织和管理自己的设计。

图4.30 ISE工程管理器界面

ISE提供了许多示例工程,这些工程都存放在ISE文件当中,可以通过File->Open Example来打开。

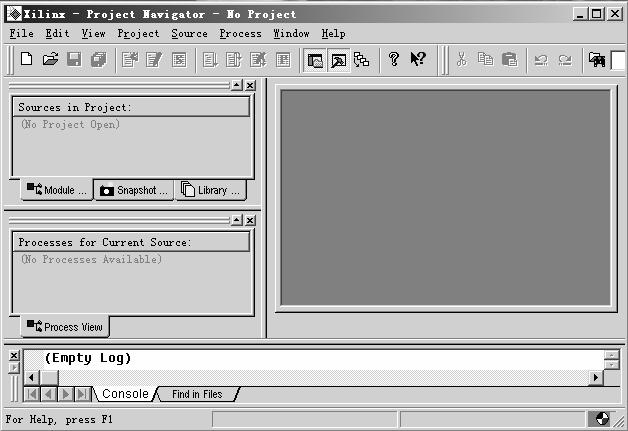

ISE为我们提供了一个很有特色的工具,那就是语言辅助模板(Language Templates)。点击Edit->Language Templates,可以调用语言辅助模板,其界面如图4.31所示。

图4.31 ISE语言辅助模板示意图

在语言模板中存放了很多HDL语言的通用语法结构和使用范例,特别是许多根据Xilinx器件IP核与硬件原语编写的实例化程序。使用语言模板,可以方便地把这些语法结构和范例插入到设计者自己的代码文件中,大大方便了程序的编写,提高了工作效率。语言模板按照ABEL、COREGEN、UCF、Verilog和VHDL的顺序存放在模板视窗中。其中COREGEN的UCF是ISE 5.x新增辅助模板。COREGEN模板由两个目录组成,分别存放当前工程中生成的IP核的Verilog和VHDL实例化文件,基内容与IP核生成器生成IP核时自动生成的实例化文件(.veo,.vho)相同。UCF模板也分成两个目录,依次存放CPLD和FPGA的用户约束文件(.ucf)的约束范例。这个模板使手工编辑UCF文件更加容易。

ABEL、Verilog和VHDL三大语言模板大致可以分为下列4个项目:

(1)器件例化(Component Instantiation):该模板仅存在于Verilog和VHDL中,给出了块RAM(Block RAM)、数字时钟延迟锁相环(Clock DLL)、数字时钟管理单元(DCM)、分布式RAM/ROM(Distributed RAM/ROM)、全局时钟缓冲(Global Clock Buffer)、查找表(LUT)、基于查找表的移位寄存组(SRLUT)、I/O器件、乘法器和选择器(MUX)等器件模块的实例化范例。

(2)语法模板(Language Templates):该模板给出了基本语法规则和应用范例。

(3)综合模板(Synthesis Templates):该模板给出了可综合实现的一些基本单元模块的范例,如乘法器、计数器和触发器等。

(4)用户模板(User Templates):该模板存放用户自己创建的特定结构,是语言模板的功能扩展。

4 ISE综合使用实例

在NBA篮球比赛中有一个24秒进攻规则,即从获取球权到投篮击中篮板、篮框、命中或投篮被侵犯,其有效时间合计不能超过24秒,否则被判违例,将失去球权。在此过程中,设置24秒、启动倒计时、暂停倒计时或者中途终止24秒(即球权归对方)均由裁判控制。本实例就是设计一个用于篮球比赛的24秒倒计时器,并且为了模拟现场比赛情况,系统中设置了24秒预设键K1、倒计时启动键K2和倒计时暂停键K3,并将计时精度设置为0.1秒。各按键具体功能如下:K1键按下,LED灯显示24秒;K2键按下,倒计时;K3键按下,计时停止。

1)新建一个工程(Project)

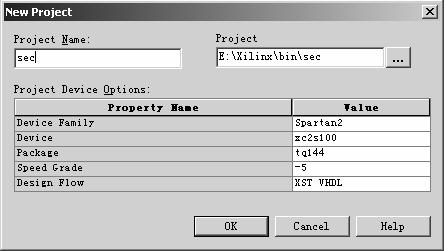

选择File / New Project命令,在图4.32所示对话框中输入工程名和工程目录,并设置器件参数。本设计使用的器件为Spartan2,xc2s100,tq144,-5。使用VHDL硬件描述语言编程。点击OK按钮确认。

图4.32 新建工程对话框

2)建立和编辑VHDL源文件

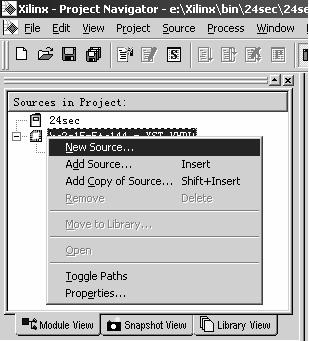

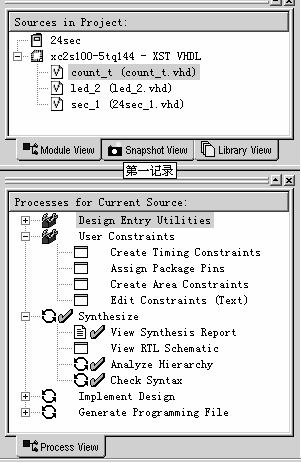

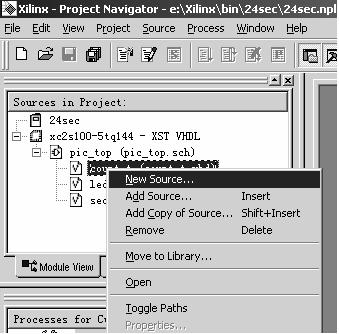

选中工程,点右键选New Source选项(如图4.33所示),添加文件count_t.vhd,led_2.vhd,sec_1.vhd(如图4.34所示)。并在文件中输入相应的VHDL程序。

图4.33 添加文件对话框

图4.34 新建VHDL文件对话框

本设计中将要用到的VHDL源程序如下:

|

count_t.zip |

3)逻辑综合(Synthesize)

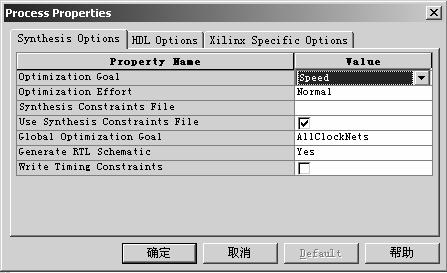

选中Synthesize选项,点![]() 进行参数设置,

进行参数设置,![]() 可以对任何操作进行参数设置。设置完成后,双击Synthesize选项,或右键选择Run选项。对其他两个VHDL程序进行同样的操作。

可以对任何操作进行参数设置。设置完成后,双击Synthesize选项,或右键选择Run选项。对其他两个VHDL程序进行同样的操作。

图4.35 综合参数设置示意图

图4.36 综合完成后界面

4)设计中的有关仿真

(1) 创建Testbench波形源文件

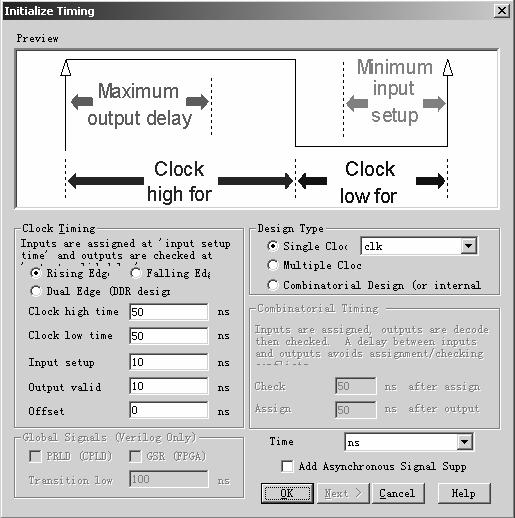

在工程项窗口Project Window的源文件中选中count_t.vhd ,用鼠标右点,在弹出的窗口中选择New Source(如图4.37所示),出现New对话框,再选择Test Bench Waveform文件类型,并输入文件名wave_1,点击下一步,再点击下一步,完成创建并进行初始化时间设置(如图4.38所示)。

图4.37 选中源文件并创建Testbench波形文件

图4.38 创建Testbench波形文件的初始化时间设置

(2) 设置输入信号初始值

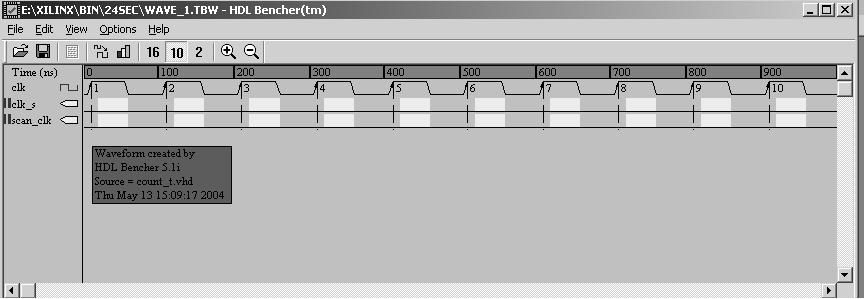

根据被仿真模块的设计要求,对各个输入信号进行初始化设置(如图4.39所示)。初始化设置完毕后将testbench文件存盘,这时HDL Bencher会提示我们设置希望仿真的时钟周期数(默认值为1),设置完毕后点击OK退出HDL Bencher。

图4.39 输入信号的初始设置