在系统编程(ISP)器件是在20世纪90年代出现的最先进的可编程器件,它无须编程,可通过PC机经下载电缆直接对安装在用户目标版上的ISP器件重复编程,实现系统重构,它给电子产品的设计和产生带来了革命性的变化。

ISP synario System是Lattice半导体公司的ispLSI系列器件的开发软件,软件内除了基本逻辑器件库外,还有一个较为完善的宏(MACRO)器件库,每一个宏器件是一组预先编好存放在库中的逻辑方程,它代表一个逻辑模块,设计时可作为逻辑器件调用。充分利用宏器件可以使逻辑设计大大简化。

在进行复杂逻辑系统设计时,可以将整个系统划分为若干模块,而每个模块还可划分为若干子模块,设计时可由底层模块开始向上逐级设计、调试(或仿真),最后进行顶层组装调试。逻辑系统中的子模块可以直接用ABEL-HDL语言编辑,也可直接由电路图编辑而成。以下简要介绍利用ispLSI1032E器件构成的数字钟控系统。

1 数字钟控系统的基本结构

数字钟控系统结构框图如图1所示,数字钟部分由秒、分、时计数电路,上、下午(A/P)转换电路,译码显示电路以及校时电路等组成。七只LED数码管分别显示上、下午和时、分、秒。钟控部分由二—十进制译电路,时间选择矩阵电路,定时电路以及发声电路等组成。脉冲信号发生器提供秒脉冲和发声高频振荡源。整个系统除了系统控制开关、脉冲信号发生器、发声电路以及LED数码管外,其余部分(如虚线框内所示)全部在一片ispLSI1032E内实现。

图1 数字钟控系统结构框图

2 数字钟在ispLSI1032E内的实现

数字钟内核心部分是时、分、秒计数器,选用宏器件中的两位十进制递增计数器CDU38分别构成时、分、秒计数器。CDU38是一个由ABE-HDL语言编辑的两位十进制递增计数器,其逻辑符号及功能表如图2所示。输出端:Q7~Q0以8421BCD码形式输出两位十进制数,CAO为进位输出端。输入端:CLK为脉冲输入端(上跳沿触发),CD为清零端,CAI为进位输入(计数容许)端,EN为选片使能端,LD为同步置数控制端,D7~D0为置数输入端。可以通过“反馈置数”方式利用宏器件CDU38组成100以内的任意进制计数器。

图2 宏器件CDU38的逻辑符号(a)和功能表(b)

2.1 秒计数模块

秒计数器为一60进制递增计数器,将CDU38的输出端Q6、Q4、Q3、Q0通过与门2控制置数控制端LD,因为置数输入端D7~D0全部接“地”,所以当计数器从0计数至59时,LD端为高电平,为置数做好准备。同时进位输出CAO(取自LD端)也为高电平,可用做高位计数器的级连信号。当第60个脉冲到来时,计数器置零,实现60进制计数。秒计数器子电路如图3所示,图中输出端Q7~Q0采用总线表示方式,其模块符号见图8数字钟模块中I-8。

图3 秒计数器子电路

2.2 分计数模块

分计数器子电路如图4所示,其模块符号见图8数字钟模块中I-7。分计数器也是一个60进制递增计数器,其构成思路与秒计数器相同,不再赘述。在分计数子电路中为CDU38输出端配接了两个输出高电平有效的BCD7段显示译码子模块(TTL47GB),可直接驱动7段显示LED数码管。输出高电平有效的BCD7段显示译码子模块符号与用ABEL—HDL语言编写的子程序如图5所示。

图4 分计数器子电路

图5 BCD7段显示译码电路模块符号与子程序

2.3 时计数模块

时计数器子电路如图6所示,其模块符号见图8数字钟模块中I-5。时计数器也是利用CDU38通过“反馈置数”方式构成。采用12小时计时制,Q4、Q1经与门I19和I11接止LD端,计数之间采用同步级连方式,当Q4和Q1为“1”且进位输入端CAI(接分计数器进位输出CAO)为高电平,此时对应时间为12时59分59秒,这时CDU38的LD端为高电平,而D7~D1接“地”,D0接高电平,因此在下一个秒脉冲到来之时,时计数器数值为01(分、秒计数器均为00),实现12进制计数。

图6 时计数器子电路

与门I18的作用是当时间为为11时59分59秒时经CAO12端输出一高电平,用来控制上下午(A/P)的转换。

2.4 上下午(A/P)转换模块

图7为A/P转换模块符号与用ABEL-HDL语言编写的子程序,模块输出端A~G直接与7段显示LED数码管相连,用来显示A或P。数码管显示A时输出端AMO为高电平,显示P时为低电平,用于时间选择控制。输入端XZ控制A、P显示,输入高电平显示A,低电平显示P。MD为灭灯控制,当计时采用24进制时,MD接低电平,A~G输出全部为“0”,实现灭灯。模块输入输出逻辑关系如图7真值表(truth_table)所示。

图7 A/P转换电路的模块符号与子程序

2.5 数字钟的组装

对秒、分、时计数模块进行组装后形成的数字钟子电路如图8所示,其模块符号见图11中I-2。秒、分、时计数器及A/P转换电路之间采用同步级连方式,秒脉冲同时引入各计数器时钟输入端(CLK),利用低位计数器的进位输出端(CAO)通过或门控制高位计数器计数容许端(CAI)。或门另一输入端通过加高电平实现校时功能,TF、TS、TAP分别作为分、时、A/P的校对控制端。

图8 数字钟子电路

3 时控系统的设计

时控系统由二一十进制译码电路、时间选择矩阵组成。

3.1 二—十进制译码电路

二—十进制译码电路采用ABEL-HDL语言编写而成,其输入端(A0~A3)接计数器输出的8421BCD码,输出端Y0~Y9各对应一组输入BCD码,高电平有效,其电路模块符号与子程序如图9所示,用来实现时间选择。

图9 二—十进制译码电路的模块符号与子程序

3.2 时间选择矩阵

时间选择矩阵子电路如图10所示,其模块符号见图11钟控系统中I-1。子电路的输入端FO[7:0]分别接时钟分计数器输出端Q7~Q0,SO[4:0]分别接时计数器输出Q4~Q0,输入端AM接A/P转换电路的输出端AMO,用“1”和“0”状态来区别上、下午。利用AM配合时、分译码器的输出,经与门进行选择,可选定24小时内任意时刻(本电路只选择到分)。图10中人的时间选择矩阵是一个学校上下课自动打铃系统,各与门所选择的时间如图所示,与门输出经或门处理后通过输出端BSH启动打铃系统。

图10 时间选择矩阵子电路

图11 钟控系统

4 数字钟控系统构成

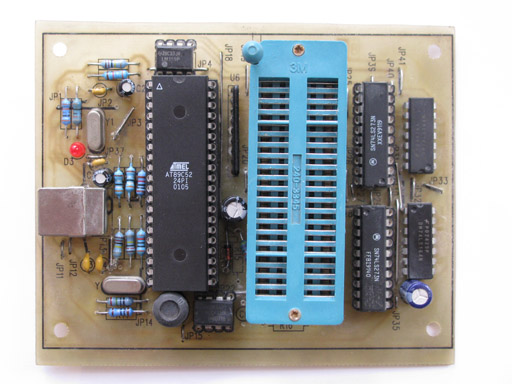

在ISP Synario System原理图编辑窗口中将数字钟与时间选择矩阵连接后构成的钟控系统如图11所示。将输入、输出端定义完毕,对系统进行编译并形成JED文件,然后下载到芯片ispLSI1032E-70PLCC84中。

输入端TAP、TS和TF通过外加高电平实现A/P、时、分校正,CD和CAI通过外加高电平实现清零和计时容许控制。系统由CLK端输入2Hz脉冲经D触发器I47分频,产生秒脉冲供数字计时。由GP端输入高频脉冲信号经D触发器I46分频在与门I60控制下推动扬声器发声。BK端通过输入高电平选通与门I60实现发声控制端。输出端MQ7~MQ0通过两片74LS48驱动两只7段显示数码管作秒显示。XF13~XF0直接驱动两只数码管作分显示。SQ7~SQ0通过两片74LS48驱动两只数码管作时显示。输出端AA~AG驱动一只数码管做A/P显示。用BSH端定时输出高频脉冲经功放电路驱动扬声器发声模拟打铃。

系统上电后,首先将数字钟校准,BK端输入高电平,当选定时刻到来时时间选择矩阵I1输出端BSH由低电平上跳为高电平,D触发器I58输出高电平,选通与门I60,扬声器发声。发生持续时间由二—十进制译码I3设定,本系统设定时间为5秒,当发声时间持续至5秒时,Y5端输出低电平,关闭与门I60,发声停止。

5 结束语

以上介绍了利用CPLD器件ispLSI1032E采用在系统编程技术构成数字钟控系统的基本过程,本系统在东南大学SE-3型ISP数字实验机上通过仿真实验,只要设计出印刷电路板即可使该系统成为实际产品。实践证明,在系统编程技术与新型可编程逻辑器件的结合,可以将一个复杂的数字系统大部分功能在一片CPLD器件内实现,这不仅简化了数字系统的设计过程,而且大大减少了系统所用器件的数量,提高了系统的可靠性与性价比。